E-ISSN: 2708-454X P-ISSN: 2708-4531 IJRCDS 2024; 5(1): 28-32 © 2024 IJRCDS www.circuitsjournal.com Received: 10-12-2023 Accepted: 08-01-2024

#### Zaineb Jebri

Institute of Electronics, Microelectronics and Nanotechnology (IEMN), Villeneuve d'Ascq, France

# Security implications of spintronic associative memory hardware

# Zaineb Jebri

#### Abstract

This review article explores the security implications associated with the emerging technology of spintronic associative memory hardware. As the demand for faster, higher-capacity, and more energy-efficient memory solutions grows, spintronics offers a promising avenue. However, integrating this technology into the computing infrastructure introduces new security challenges and considerations. This paper examines the unique vulnerabilities of spintronic memory devices, potential attack vectors, and the strategies for safeguarding them against cyber threats, thereby providing a roadmap for secure spintronic memory development.

Keywords: Security implications, spintronic associative, spin transport electronics

#### Introduction

Spintronics, short for spin electronics or spin transport electronics, represents a fascinating field of research and innovation that intersects quantum physics and technology, focusing on the intrinsic spin of the electron and its associated magnetic moment, in addition to its fundamental electronic charge. This approach stands in contrast to traditional electronics, which relies solely on the charge of electrons for information processing and storage. The exploration and application of spintronics have significant implications for memory technology, heralding a new era of computing devices with enhanced capabilities, efficiency, and performance. Spintronics exploits the spin property of electrons—a quantum feature representing angular momentum and a magnetic moment. In spintronics, the spin state (up or down) of electrons in a material can represent binary data (0s and 1s). This concept opens up new pathways for creating memory devices that operate differently from traditional charge-based electronics.

## **Main Objective**

To explain and understand the Security Implications of Spintronic Associative Memory Hardware.

#### Security Challenges in Spintronic Memory Devices

Spintronic memory devices, heralded for their nonvolatility, speed, and energy efficiency, also introduce unique security challenges. These challenges stem from the novel mechanisms of data storage and processing inherent to spintronics.

Below, we delve into specific security challenges associated with spintronic memory devices;

## **Data Remanence and Secure Deletion**

Data remanence refers to the residual representation of digital data that remains even after attempts have been made to erase or remove the data. In the context of digital memory devices, including those based on spintronic technology, data remanence poses a significant security risk, particularly when sensitive information needs to be irretrievably deleted. Secure deletion, therefore, involves processes and methods designed to eliminate the possibility of recovering any residual data. Spintronic devices, such as Magnetoresistive Random-Access Memory (MRAM), leverage magnetic properties to store data. Unlike traditional volatile memory, which requires electric power to maintain stored information, spintronic memory retains data without power, thanks to stable magnetic states.

Corresponding Author: Zaineb Jebri Institute of Electronics, Microelectronics and Nanotechnology (IEMN), Villeneuve d'Ascq, France This nonvolatility, while advantageous for energy efficiency and data persistence, complicates the secure deletion of data due to the inherent stability and durability of the magnetic states used for data storage.

Several following studies have focused on the challenges of data remanence in non-traditional memory technologies;

Jiang *et al.*, 2012 <sup>[9]</sup>, focused on flash memory, this study highlights techniques like overwriting and cryptographic erasure, which could be adapted for spintronic devices. The effectiveness of these methods in flash memory suggests a potential pathway for addressing data remanence in spintronics, albeit with modifications to account for the magnetic nature of data storage.

Halderman *et al.*, 2009<sup>[7]</sup>, demonstrated that data could be recovered from volatile memory types under certain conditions. While not directly related to spintronics, this study underscores the broader issue of data remanence across memory technologies and the need for secure deletion protocols.

A study by Chappert *et al.*, 2007 <sup>[10]</sup>, delved into the principles of magnetic storage at a quantum level, touching upon the stability and resilience of magnetic states. These findings are critical for understanding why spintronic memory devices might resist conventional data wiping techniques, thereby necessitating novel approaches to secure deletion

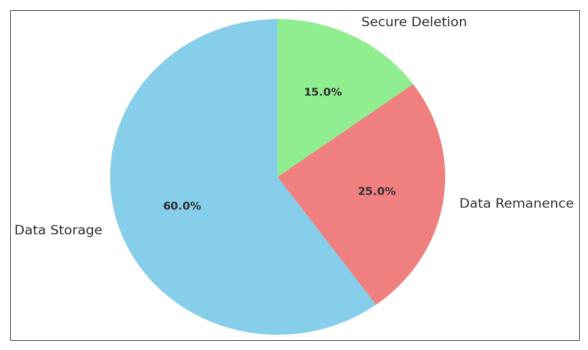

Fig 1: Data remanence and secure deletion in spintronic devices

The diagram succinctly underscores the challenges and necessities in managing data securely in spintronic memory devices. The significant portion of data remanence (25%) points to a critical security challenge; not all data that users attempt to delete is necessarily removed thoroughly, leaving sensitive information potentially accessible.

This issue is compounded in spintronic devices due to their non-volatile nature and the stability of the magnetic states used for storing data. Thus, while the capacity and efficiency of spintronic memory are highlighted by the large portion of data storage, the segments dedicated to data remanence and secure deletion emphasize the need for innovative solutions in data management and security.

The need for secure deletion (15%) indicates ongoing efforts and the importance of developing effective methods to mitigate the risk of data remanence. This reflects the research and development focus in the field of spintronics to enhance the security of these devices, ensuring that when data is meant to be deleted, it is done so in a manner that makes it irrecoverable, thereby protecting sensitive information.

#### Side-Channel Attacks

Side-channel attacks exploit indirect information leakage from a computing device to uncover sensitive data, such as cryptographic keys or personal information, without directly attacking the encryption algorithm or the data itself. These attacks analyze observable physical phenomena-such as power consumption, electromagnetic emissions, timing information, and even sound-that correlate with the device's internal operations. In the context of spintronic memory devices, unique characteristics related to the manipulation and storage of electron spins could potentially offer new side-channels for attackers to exploit.

Several following studies across different technologies have highlighted the vulnerability of electronic devices to sidechannel attacks;

Kocher *et al.*, 1999 <sup>[2]</sup>, introduced Simple Power Analysis (SPA) and Differential Power Analysis (DPA) attacks, demonstrating that variations in power consumption during cryptographic operations could reveal secret keys. While not specific to spintronics, this foundational work underpins the potential for similar vulnerabilities in spintronic devices.

Agrawal *et al.*, 2002 <sup>[6]</sup>, showed that electromagnetic emissions from electronic devices during cryptographic operations could be analyzed to extract secret keys, suggesting that any device, potentially including spintronic memory, emitting such signals could be at risk.

Genkin *et al.*, 2014 <sup>[11]</sup>, demonstrated that sound emitted by a computer during operations could be exploited to extract encryption keys, underscoring the broad spectrum of side-channels available to attackers.

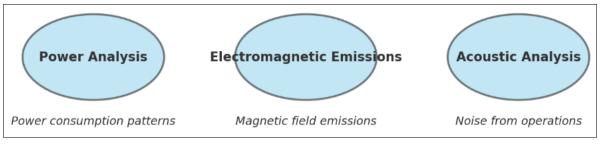

Fig 2: Side-channel attacks vectors on spintronic devices

The diagram effectively encapsulates the multi-faceted nature of side-channel threats facing spintronic memory devices, illustrating that securing these devices extends beyond protecting the data and algorithms they use. It highlights the need for a holistic security approach that considers not just direct attacks but also the indirect pathways through which sensitive information might be inferred. Moreover, the diagram suggests that mitigating side-channel attacks on spintronic devices involves both technological solutions-such as improved device designs that reduce or mask emissions-and operational practices, like environmental controls to limit the effectiveness of external monitoring. In conclusion, while spintronic memory devices promise significant advantages in terms of performance and efficiency, the diagram emphasizes the complexity of ensuring their security. It showcases the necessity for ongoing research and development aimed at understanding and countering the unique side-channel vulnerabilities these innovative devices introduce.

#### **Fault Injection Attacks**

Fault injection attacks involve deliberately causing errors in a device's hardware or software to circumvent security measures or extract sensitive information. These attacks exploit the fact that errors can lead to unpredictable behavior, which might include revealing secret keys, bypassing authentication, or inducing other security vulnerabilities. Attackers can induce faults through various means, including voltage spikes, temperature variations, laser beams, or electromagnetic pulses, targeting specific components of a device to trigger desired erroneous behaviors.

Fault injection attacks have been extensively studied in the context of cryptographic devices and systems;

A seminal work by Biham and Shamir demonstrated that by inducing faults in cryptographic algorithms (e.g., AES, RSA) and analyzing the differences between correct and faulty outputs, attackers could recover encryption keys more efficiently than by brute force alone (Biham and Shamir, 1997)<sup>[1]</sup>.

Balasch *et al.*, 2011 <sup>[8]</sup>, have shown that by manipulating the clock signal of a microprocessor, one can induce operational faults that might lead to security breaches. This technique has been applied to smart cards and other embedded devices to bypass security checks or corrupt the execution of cryptographic algorithms.

Skorobogatov, 2005 <sup>[3]</sup>, demonstrated the use of focused laser beams to create transient faults in semiconductor devices. This method allows precise targeting of specific chip areas, enabling attackers to manipulate device behavior or extract sensitive information without physical contact.

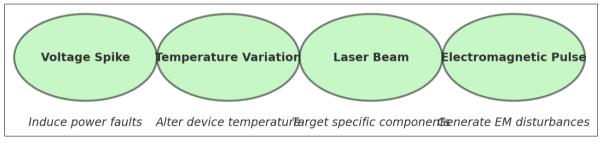

Fig 3: Fault Injection Attacks Methods

**Voltage Spike:** Voltage spikes can cause unexpected behavior in the electronic control circuits that manage spintronic elements, potentially leading to incorrect spin states or damaging the delicate quantum mechanical processes underlying spintronics. Devices must be designed with robust power regulation and protection circuits to mitigate the risks posed by voltage spikes, ensuring stable operation even under fault conditions.

**Temperature Variation:** Temperature changes can affect the magnetic properties that spintronic devices rely on, potentially leading to data loss or corruption. Spin alignment and coherence, crucial for data storage and processing, may be disrupted by thermal fluctuations. Temperature management strategies, including efficient cooling systems and thermal shielding, are essential for maintaining the integrity of spintronic devices.

Laser Beam: Impact on Spintronics: Precision targeting with a laser beam can alter local spin states, enabling attackers to manipulate data storage and processing functions directly. This method's precision poses a significant risk, as it can be used to selectively disrupt device operations. Implementing physical barriers and protective coatings to deflect or absorb laser energy can help protect against laser-based fault injections. Additionally, monitoring for unusual photonic activity could aid in detecting such attacks.

Electromagnetic Pulse (EMP): EMPs can induce

unintended magnetic fields within spintronic devices, affecting the electron spin orientations. This could lead to widespread data corruption or alter the logic of spin-based computing processes. Shielding devices from electromagnetic interference (EMI) and designing circuits to be resilient against sudden electromagnetic fluctuations are critical countermeasures against EMP attacks.

## **Reverse Engineering and Intellectual Property Theft**

Reverse engineering in the context of electronic devices involves deconstructing and analyzing a device's hardware and software to understand its design, functionality, and operation. This process can be used for legitimate purposes, such as debugging, enhancing existing technology, or ensuring compatibility. However, it also poses significant risks of intellectual property (IP) theft, where proprietary technologies, algorithms, and designs are illegally copied or repurposed without authorization. In the rapidly advancing field of spintronics, where cutting-edge research and development are highly valued, the threat of reverse engineering and IP theft is a serious concern for innovators and companies.

Torrance and James (2009)<sup>[4]</sup> highlighted the risks and challenges associated with securing integrated circuits (ICs) from reverse engineering. They demonstrated techniques for extracting device functionalities, showcasing the vulnerabilities in even seemingly secure systems.

Tehranipoor and Koushanfar (2010) <sup>[5]</sup> discussed the insertion of hardware Trojans through the supply chain and the role of reverse engineering in detecting such vulnerabilities. This study underlines the dual nature of reverse engineering as both a threat and a tool for enhancing security. Various studies have proposed methods to protect against reverse engineering, including obfuscation techniques, the use of hardware security modules, and the implementation of anti-tamper technologies. These strategies aim to complicate the reverse engineering process, thereby protecting intellectual property.

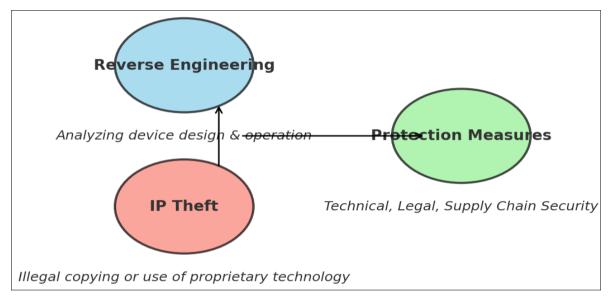

Fig 4: Reverse Engineering and Intellectual Protection in Spintronics

**Reverse Engineering:** Illustrated in sky blue, this component sits at the top, signifying the starting point of the process where the device's design and operation are analyzed. This step is fundamental and can be driven by curiosity, competitive analysis, or malicious intent. In spintronics, where devices operate on cutting-edge principles, reverse engineering can reveal valuable insights into novel materials, quantum behaviors, and unique electronic configurations.

**IP Theft:** Shown in salmon, this represents the potential outcome of reverse engineering when conducted with malicious intent. It involves the illegal copying or exploitation of proprietary technology, which could be particularly damaging in the field of spintronics due to its innovative nature and the significant research and development investments involved. The arrow leading from reverse engineering to IP theft underscores the risk that, if left unchecked, analytical efforts could lead to unauthorized use or duplication of proprietary technologies.

**Protection Measures:** Depicted in light green, this component is positioned to intercept the progression from

reverse engineering to IP theft. It encompasses a variety of strategies-technical, legal, and through supply chain security-to safeguard against unauthorized access and use of proprietary information. In the spintronics context, technical measures could include encryption, obfuscation, and physical security features designed to complicate reverse engineering efforts. Legal measures involve patents, copyrights, and trade secrets, while supply chain security ensures the integrity of the manufacturing and distribution processes.

The arrow from IP Theft to Protection Measures illustrates a feedback loop where the experience and knowledge of potential IP theft inform the development and implementation of more robust protection strategies. This dynamic highlights the ongoing battle between advancing technology and the need to protect intellectual property.

## Conclusion

The study of the security implications of spintronic associative memory hardware illuminates the multifaceted nature of protecting advanced technological innovations. As spintronics moves closer to widespread adoption, addressing these security challenges becomes paramount. The development of spintronic devices must therefore proceed hand in hand with the advancement of security measures tailored to their unique vulnerabilities.

This journey towards secure spintronic technologies is not solely the responsibility of researchers and developers; it also requires collaboration across the cybersecurity community, policymakers, and industry stakeholders. By fostering an ecosystem that prioritizes security as a fundamental component of innovation, the potential of spintronic associative memory hardware can be fully realized, benefiting the future of computing while safeguarding against the evolving landscape of cyber threats.

In conclusion, as we stand on the brink of a new era in memory technology, the insights gained from this study highlight the importance of vigilance, innovation, and collaboration in securing the future of spintronics.

## References

- Biham E, Shamir A. differential fault analysis of secret key cryptosystems. In: Proceedings of the 17<sup>th</sup> Annual International Cryptology Conference on Advances in Cryptology; 1997 Aug 17-21; Santa Barbara, California. Berlin: Springer; c1997. p. 513-25.

- Kocher P, Jaffe J, Jun B. Differential Power Analysis. In: Proceedings of the 19<sup>th</sup> Annual International Cryptology Conference on Advances in Cryptology; 1999 Aug 15-19; Santa Barbara, California. Berlin: Springer; c1999. p. 388-397.

- Skorobogatov S. Semi-invasive attacks A new approach to hardware security analysis. Technical Report UCAM-CL-TR-630. Cambridge: University of Cambridge, Computer Laboratory; c2005.

- Torrance R, James D. The state-of-the-art in semiconductor reverse engineering. In: Proceedings of the 46<sup>th</sup> Annual Design Automation Conference; 2009 Jul 26-31; San Francisco, California. New York: ACM; c2009. p. 333-338.

- 5. Tehranipoor M, Koushanfar F. A Survey of Hardware Trojan Taxonomy and Detection. IEEE Design & Test of Computers. 2010;27(1):10-25.

- Agrawal D, Archambeault B, Rao JR, Rohatgi P. The EM Side-Channel(s). In: Kaliski BS Jr., Koç ÇK, Paar C, editors. Cryptographic Hardware and Embedded Systems - CHES 2002. Lecture Notes in Computer Science, vol 2523. Berlin: Springer; c2003. p. 29-45.

- Halderman JA, Schoen SD, Heninger N, Clarkson W, Paul W, Calandrino JA, *et al.* Lest We Remember: Cold Boot Attacks on Encryption Keys. In: Proceedings of the 18<sup>th</sup> USENIX Security Symposium; 2009 Aug 10-14; Montreal, Quebec. Berkeley: USENIX Association; c2009. p. 45-60.

- Balasch J, Gierlichs B, Grosso V, Reparaz O, Verbauwhede I. Theory and Practice of a Leakage Resilient Masking Scheme. In: Lee DH, Wang X, editors. Advances in Cryptology - ASIACRYPT 2011. Lecture Notes in Computer Science, Vol. 7073. Berlin: Springer; c2011. p. 758-775.

- 9. Jiang K, Lepak DP, Hu J, Baer JC. How does human resource management influence organizational outcomes? A meta-analytic investigation of mediating mechanisms. Academy of management Journal. 2012 Dec;55(6):1264-94.

- 10. Chappert C, Fert A, Van Dau FN. The emergence of

spin electronics in data storage. Nature materials. 2007 Nov;6(11):813-23.

11. Genkin D, Ishai Y, Prabhakaran MM, Sahai A, Tromer E. Circuits resilient to additive attacks with applications to secure computation. In proceedings of the forty-sixth annual ACM symposium on Theory of computing; c2014. p. 495-504.